DVC User Manual

version V1.2,2025 ————CAD

DVC User Manual一、DVC目录层次结构命名规范1. Phase(阶段)2.Block(模块)3.Stage(步骤)4.Version(版本)5.DVC SVN关系图二、环境配置与dvc命令执行前提加载环境变量:source /lyg/projects/<project_code>/cshrc_dop三、DVC应用场景1.项目DVC初始化(for PM/CAD/Engineer)1.1 For PM —项目前夕准备 1.2 For CAD —项目DVC初始化操作命令(仅限<Project_ID>aa00账号)1.3 For Engineer Member —项目DVC初始化2.For Engineer Member2.1 如何将设计好的资料上传至DVC(for:上家/要将设计数据传递出去的designer)2.2 如何从DVC中获取资料(for:下家/要承接前一步骤数据的designer)2.3 如何通过DVC让自己的team member统一使用指定资料(for:Team Leader)3.For PL —审批设计版本资料四、Native Commands底层支持与高级数据管理1.Native Commands与Wrapper Commands对照2.导入外部数据到DVC设计仓库3. 分步骤管理设计文件夹(多步骤流程)4. 多模式管理设计文件夹(多工艺角/电压模式)五、异常处理与维护1.常见错误与解决2.数据版本查看与版本恢复六、个人扩展建议自动化脚本示例:多项目管理:七、总结

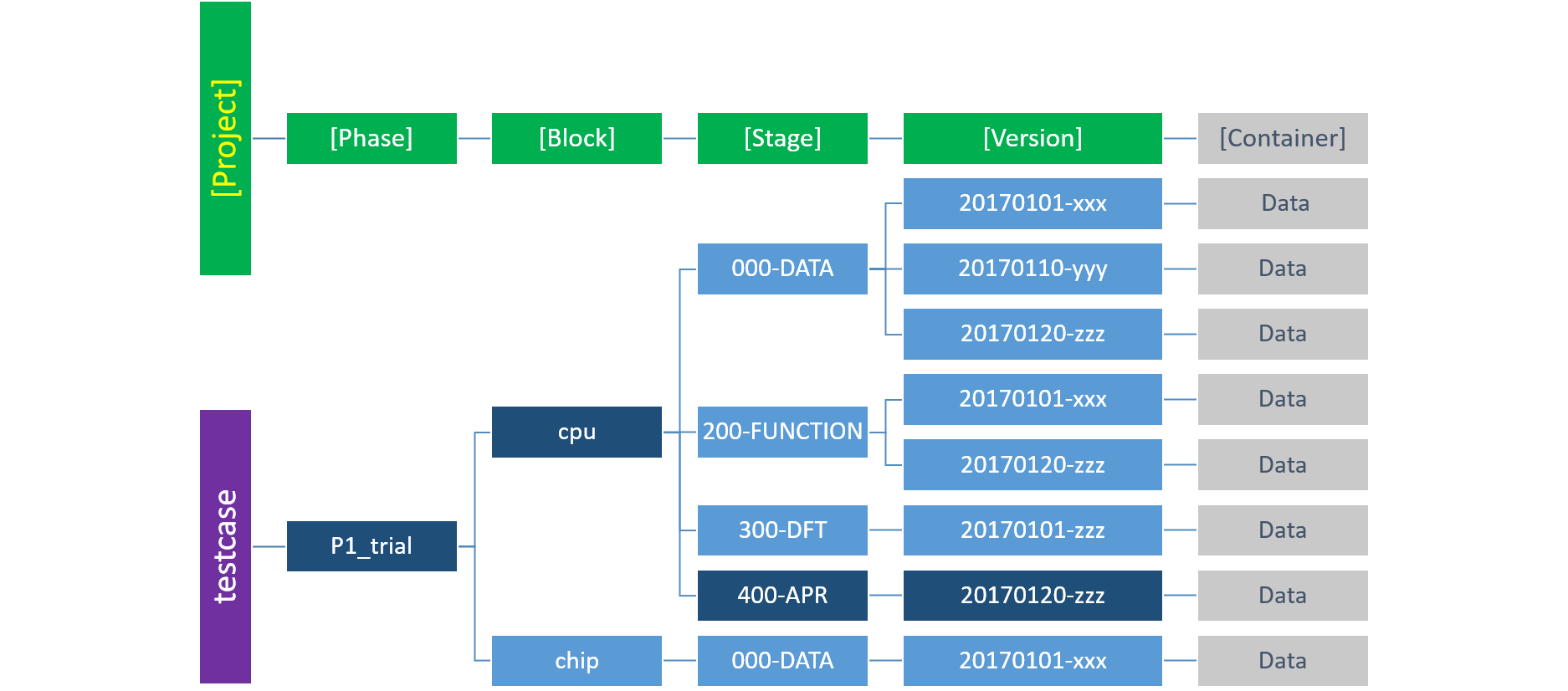

一、DVC目录层次结构命名规范

DVC通过4层基础目录结构管理设计数据,每层命名需严格遵循规范以确保统一性。 层级依次为:Project(项目):

1.Phase(阶段)

2.Block(模块)

3.Stage(步骤)

4.Version(版本)

以下是各层级的详细规则及示例:

1. Phase(阶段)

定义:划分项目生命周期,由项目经理(project manager)定义。

命名规则:

格式:P<数字>-<阶段描述>,数字从1开始递增。

示例:

| PhaseID | Phase Name (阶段名称) | Phase Title |

|---|---|---|

| S4 | S4-presale | Project Firmed |

| P0 | P0-kickoff | Project Kicoff |

| P1 | P1-trial | Initial Design Trial Run |

| P2 | P2-stable | Stable Design Implementation |

| P3 | P3-final | Final Design Implementation |

| P4 | P4-tapeout | Design Tapeout for Wafer Fabrication |

| P5 | P5-pilot | Pilot Run Test with Assembled Chip |

注意事项:

阶段名称需全局唯一,不可重复。

推荐使用标准名称,非特殊情况不自定义。

2.Block(模块)

定义:划分设计的功能模块,由设计经理(design manager)定义。

命名规则:

格式:小写英文缩写

示例:

| 模块名称 | 描述 |

|---|---|

| top | 顶层芯片模块 |

| cpu | CPU核心模块 |

| ddr | DDR控制器模块 |

| sub1 | 子模块1 |

注意事项:

模块名称需与物理设计层次对齐。

避免使用特殊字符(如 _, – )。

3.Stage(步骤)

定义:标识设计流程的里程碑节点,区分数据输入/输出,由团队负责人基于使用的工具执行流程(tool execution flow)定义。

命名规则:

格式:<三位数字>-_<用途>_<类型>

示例:

| Stage 名称 | Description | Sub-Stages |

|---|---|---|

| 000-DATA | Initial Design Data | 010-doc, 020-flow, 030-pdk, 040-library, 050-design |

| 100-CIRCUIT | Circuit Design & Simulation | 110-spice, 120-layout, 130-lpe |

| 200-LOGIC | Logic Design & Simulation | 210-simulation, 220-synthesis, 230-formal |

| 300-DFT | Design For Test | 310-jtag, 320-scan, 330-mbist, 340-lbist, 350-atpg |

| 400-APR | Physical Implementation | 410-floorplan, 420-place, 430-cts, 440-route, 450-opt_timing, 460-opt_power, 470-eco |

| 500-TIMING | Design Signoff | 510-rcxt, 520-sta, 530-power, 540-ir_drop, 550-noise, 560-thermal, 570-reliability |

| 600-POWER | Tapeout | 610-drc, 620-dfm, 630-lvs, 640-erc |

| 700-TAPEOUT | Die & Chip Testing | 710-wafer_probe, 720-final_test |

| 800-TESTING | Package Design | |

| 900-PACKAGE | System Validation |

自定义规则:

允许在Stage下创建子Stage(如330-mbist)。

4.Version(版本)

定义:同一Stage下的设计版本,由设计工程师(designer)命名。

命名规则:

格式:<DBSRC_DATE>–<用途>_<子版本>,日期格式为YYYYMMDD。

示例:

| 版本名称 | 描述 |

|---|---|

| 20240501-scan_v1 | 2024年5月1日提交的扫描链版本1 |

| 20240615-apr_eco_v2 | 2024年6月15日提交的APR ECO版本2 |

| 20240701-tapeout_final | 2024年7月1日最终流片版本 |

注意事项:

日期必须与客户提供的网表日期一致。

子版本号从V1开始递增,禁止跳号。

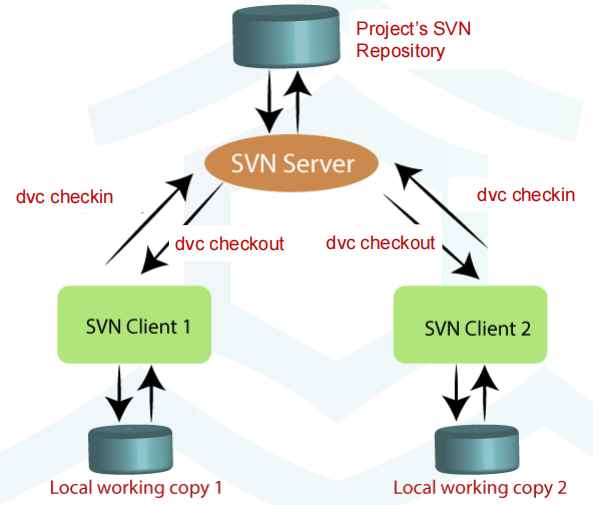

5.DVC SVN关系图

二、环境配置与dvc命令执行前提

加载环境变量:source /lyg/projects/<project_code>/cshrc_dop

重要性:

路径映射:设置项目根目录(/projects/<project_code>)和默认工作目录(DVC_WORKING)。

权限验证:绑定用户账号与角色权限(如a00为项目经理,f为前端工程师)。

服务器配置:定义SVN服务器地址($SVN_HOST)和端口($SVN_PORT)。

未加载的后果:

路径混乱:DVC系统将默认使用$HOME/DVC目录,可能导致数据分散。

权限错误:无法访问SVN仓库,提示Permission denied或Repository not found。

命令失效:无法识别$pCode,需手动输入完整路径(如svn://server:port/project)。

三、DVC应用场景

以下以项目 d1tl409a 为例,结合层次结构命名规范,展示完整操作流程:

1.项目DVC初始化(for PM/CAD/Engineer)

1.1 For PM —项目前夕准备

当已建立对应项目账号后,请联络CAD部门的谢嘉明(Drin),进行项目的DVC初始化。

1.2 For CAD —项目DVC初始化

目标:1.搭建&加载DVC环境 2.创建项目SVN仓库

操作命令(仅限<Project_ID>aa00账号)

**Step 1:加载环境变量> source /lyg/projects/d1tl409a/cshrc_dop **Step 2: 创建项目SVN仓库> dvc project setup1.3 For Engineer Member —项目DVC初始化

目标:1.确定项目开始的时间(EX:可以客户提供资料的日期作为golden date)

2.制定划分相应的Phase&block&stage&version

3.将initial data checkin到dvc的对应项目仓库

Engineer Member使用各自的项目账号进行操作(以项目d1tl409a为例)

x**Step 1:加载环境变量> source /lyg/projects/d1tl409a/cshrc_dop**Step 2:建立该项目DVC的working space> dvc project checkout**Step 3: 建立相应的DVC目录结构> dvc folder create <PHASE>/<BLOCK>/<STAGE>/<VERSION> EX: dvc folder create P1-trial/cpu/000-DATA/20240305-release_v1**Step 4:将initial data 上传到项目svn仓库* Step4.a:先将svn仓库的相应目录同步到本地的'工作文件夹'里#'工作文件夹'可以使用'setenv DVC_WORKING <path>'指定,于step2之前,之后需再进行一次step2> dvc folder checkout <PHASE>/<BLOCK>/<STAGE>/<VERSION> EX: dvc folder checkout P1-trial/cpu/000-DATA/20240305-release_v1#只要进行了‘dvc folder checkout’的操作,接下来的其他操作都是对您checkout到本地的目录进行的。* Step4.b:将initial data复制到本地的目标目录中#类似于cp命令,sourcefile_path为您想复制的文件/目录的路径, targetfile_name为您复制到'checkout出来的目录'的文件/目录的名字#> dvc object copy sourcefile_path targetfile_name EX: dvc object copy CPU_20240305 CPU_20240305* Step4.c:将复制到‘checkout到本地的目录’里的数据同步上传至svn#checkin的'<PHASE>/<BLOCK>/<STAGE>/<VERSION>'与您上一步chekout的是一样的> dvc dvcpath checkin <PHASE>/<BLOCK>/<STAGE>/<VERSION>EX: dvc folder checkin P1-trial/cpu/000-DATA/20240305-release_v1建议:DVC初始化时,将协商划分好的所有Phase和block都使用'dvc folder create'于DVC仓库内建好,方便工程师们能第一时间将数据上传同步。

注:1.Phase名称具体可看 2.Block名称具体可看 3.Stage名称具体可看 4.Version名称具体可看 DVC user guide

2.For Engineer Member

2.1 如何将设计好的资料上传至DVC(for:上家/要将设计数据传递出去的designer)

例如:前端工程师提交CPU模块功能设计(Block: cpu, Stage: 200-LOGIC)。

目标:提交CPU功能设计数据至Version 20240501-logic_v1。

完整提交设计数据流程命令(完成CPU模块功能设计的工程师执行):

xxxxxxxxxx# Step 1:加载环境变量> source /lyg/projects/d1tl409a/cshrc_dop# Step 2:建立该项目DVC的working space> dvc project checkout# Step 3:于DVC仓库中创建Version目录> dvc folder create P1-trial/cpu/200-LOGIC/20240501-logic_v1# Step 4: 于local的'工作文件夹'内Checkout出相应的Version目录> dvc folder checkout P1-trial/cpu/200-LOGIC/20240501-logic_v1 # Step 5: 复制设计文件到'工作文件夹'内的相应Version目录里# 执行checkout操作后,所有操作都是对于您'checkout到local的目录'来进行# 执行完复制的数据只存在local,还未上传至DVC仓库#类似于cp命令,sourcefile_path为您想复制的文件/目录的路径, targetfile_name为您复制到'checkout出来的目录'的文件/目录的名字#EX:> dvc object copy sourcefile_path targetfile_name> dvc object copy /design/rtl/cpu.v cpu.v> dvc object copy /design/constraints/cpu.sdc cpu.sdc# Step 6: 将设计数据提交至DVC仓库> dvc dvcpath checkin P1-trial/cpu/200-LOGIC/20240501-logic_v1建议:Engineer将所有关键设计数据&重要报告(dqi report)等需要传递或备份的重要数据上传至DVC。

关键点:1.若需要切换或产生不同的'工作文件夹'时请使用:> setenv DVC_WORKING /projusers/d1tl409aXXX/XXX/…

> dvc project checkout(要再做一次Step2)

#建议你可以把它写在.cshrc内

2.完成相应设计后,请及时将数据上传至DVC中,并告知下家正确版本数据的路径(在DVC中的数据存放路径与您local的一致)。

2.2 如何从DVC中获取资料(for:下家/要承接前一步骤数据的designer)

例如:后端工程师获取前端数据并执行APR(Stage: 400-APR)。

目标:从200-LOGIC获取数据,进行布局布线。

命令(后端工程师):

xxxxxxxxxx# Step 1:加载环境变量&建立该项目DVC的working space> source /lyg/projects/d1tl409a/cshrc_dop> dvc project checkout# Step 2: 检出由上家提供的正确版本数据> dvc folder checkout P1-trial/cpu/200-LOGIC/20240501-logic_v1# 进行checkout操作后,所设置的'工作文件夹'下有类似以下示例的内容:. ├── :block -> /lyg/projusers/<project_id>/<project_account>/DVC/P1-trial/cpu ├── :container -> :version/. ├── DVC/ │ ├── : -> P1-trial │ └── P1-trial │ ├── : -> cpu│ └── cpu │ ├── : -> 200-LOGIC│ └── 200-LOGIC│ ├── : -> 20240501-logic_v1 │ └── 20240501-logic_v1 │ ├── XXXX_designfiles│ └── XXXX_XXXX├── :phase -> /lyg/projusers/<project_id>/<project_account>/DVC/P1-trial ├── :stage -> /lyg/projusers/<project_id>/<project_account>/DVC/P1-trial/cpu/200-LOGIC├── svn└── :version -> /lyg/projusers/<project_id>/<project_account>/DVC/P1-trial/cpu/200-LOGIC/20240501-logic_v1**下家完成设计后参考上家的Step(3~6),将相关设计数据提交至DVC仓库。建议:1.Engineer将所有关键设计数据&重要报告(dqi report)等需要传递或备份的重要数据上传至DVC。 2.建议Engineer工作在自己的stage version中,避免打乱/修改到checkout下来的上家的数据;当上家数据有所更新时,checkout数据到local后,查看相关更新信息更准确便捷。

关键点:1.需与上家确定正确的版本数据路径,避免出现版本错误问题。 2.完成相应设计后,请先创建自己的working stage version(dvc folder create)并检出到本地'工作文件夹'(dvc folder checkout),将设计数据复制到working stage version(dvc object copy)后,再上传至DVC(dvc dvcpath checkin);避免对上家的数据造成影响。

2.3 如何通过DVC让自己的team member统一使用指定资料(for:Team Leader)

例如:Team Leader先将自己的文件和上家所提交的数据整合在一个指定文件夹内,Team member们只需checkout指定的文件夹数据即可。

xxxxxxxxxxTeam Leader:# Step 1:加载环境变量&建立该项目DVC的working space> source /lyg/projects/d1tl409a/cshrc_dop> dvc project checkout#Step2.1:先将上家的数据checkout到本地'本地工作文件夹内'> dvc folder checkout P1-trial/cpu/200-LOGIC/20240501-logic_v1#Step2.2:再于DVC仓库中创建<指定文件夹>> dvc folder create P1-trial/cpu/300-DFT/20240501-init#Step2.3:将<指定文件夹>checkout到local> dvc folder checkout P1-trial/cpu/300-DFT/20240501-init#Step2.4:将上家提交的数据链接到<指定文件夹>内,于'工作文件夹'内操作> dvc object link P1-trial/cpu/200-LOGIC/20240501-logic_v1 A #EX: dvc object link sourcefilepath targetfilename 上面的A为您在<指定文件夹>内创建的软连接的名字# Step 4:将统一使用的资料(B)复制到local的<指定文件夹>内> dvc object copy .../.../B B_share(类似cp命令可对复制过来的文件改名)# Step 5:将local<指定文件夹>内的数据上传至DVC> dvc dvcpath checkin P1-trial/cpu/300-DFT/20240501-init other member: # Step 1:加载环境变量&建立该项目DVC的working space> source /lyg/projects/d1tl409a/cshrc_dop> dvc project checkout# Step 2: 将<指定文件夹>checkout到local> dvc folder checkout P1-trial/cpu/300-DFT/20240501-init# checkout到local后DVC内容示例:DVC/ ├── : -> P1-trial └── P1-trial ├── : -> cpu └── cpu ├── : -> 300-DFT └── 300-DFT ├── : -> 20240501-init └── 20240501-init ├── A -> /lyg/projusers/d1tl409a/d1tl409ac02/DVC/P1-trial/cpu/200-LOGIC/20240501-logic_v1 └── B ├── XXX_file └── XXXXXX# 完成设计后参考上家的Step(3~6),将相关设计数据提交至DVC仓库。> dvc folder create P1-trial/cpu/310-MBIST/20240501-dftout> dvc folder checkout P1-trial/cpu/310-MBIST/20240501-dftout> dvc object copy netlist.v netlist.v> dvc dvcpath checkin P1-trial/cpu/310-MBIST/20240501-dftout建议:1.Engineer将所有关键设计数据&重要报告(dqi report)等需要传递或备份的重要数据上传至DVC。 2.建议Engineer工作在自己的stage version中,避免打乱/修改到checkout下来的上家的数据;当上家数据有所更新时,checkout数据到local后,查看相关更新信息更准确便捷。

关键点:1.需与上家确定正确的版本数据路径,避免出现版本错误问题。 2.提交设计数据前,请先创建自己的working stage version(dvc folder create)并检出到本地'工作文件夹'(dvc folder checkout),将设计数据复制到working stage version(dvc object copy)后,再上传至DVC(dvc dvcpath checkin);避免对上家的数据造成影响。

3.For PL —审批设计版本资料

例如:审批CPU模块的功能设计数据。

目标:审批是否通过CPU功能设计数据。

命令(项目经理):

xxxxxxxxxx# Step 1:加载环境变量&建立该项目DVC的working space> source /lyg/projects/d1tl409a/cshrc_dop> dvc project checkout# Step 2:根据list检出并检查数据> dvc dvcpath confirmlist**输出示例: <Phase>/<Block>/<Stage>/<Version> P1-trial/block1/200-LOGIC/20240501-release_v1 P1-trial/block2/330-mbist/20240501-release_v1 P1-trial/block3/000-DATA/20240612_cust_v1 ......Please do 'dvc folder checkout' to review the stage versionIf ok, please do 'dvc dvcpath confirm', else notify the member to fix it.> dvc folder checkout P1-trial/cpu/200-LOGIC/20240501-logic_v1# Step 3:使用dqiviewer查看DQI等重要report> cd ../../20240501-logic_v1> dqiviewer# Step 3.1:审批通过> dvc dvcpath confirm P1-trial/cpu/200-LOGIC/20240501-logic_v1# Step 3.2:审批不通过,打印出提交成员信息,通知其修改> dvc dvcpath confirminfo P1-trial/cpu/200-LOGIC/20240501-logic_v1**成员信息示例: --------------------------------------------------- Member: d1tl409ad01 Web Aug 21 15:28:30 CST 2024 submit_data:P1-trial/cpu/200-LOGIC/20240501-logic_v1建议:PL需确定Engineer member提交的设计资料正确性与完整性,可以使用DQI viewer进行设计质量的检查(进入checkout下来的目录下,敲打:dqiviewer对DQI viewer进行调用)。

关键点:1.未通过PL确认的,Engineer提交的设计数据不会上传至DVC中,为避免影响项目进度,请PL及时处理。

四、Native Commands底层支持与高级数据管理

1.Native Commands与Wrapper Commands对照

| 操作类型 | Wrapper Command | Native Command | 说明 |

|---|---|---|---|

| 创建Phase | dvc folder create P1_trial | dvc_create_phase P1_trial | 项目经理初始化阶段 |

| 签入Block | dvc dvcpath checkin | dvc_checkin_block cpu | 提交模块数据 |

| 递归检出 | dvc project checkout –recursive | dvc_checkout_project | 下载全项目数据 |

| 删除Container | dvc folder remove | dvc_remove_container | 清理无效容器 |

2.导入外部数据到DVC设计仓库

目标:将外部设计数据(如客户提供的网表或工艺库)导入DVC系统,并关联到指定Version。

操作流程:

xxxxxxxxxx# Step 1: 设置SVN根目录(默认:$HOME/svn_root)> setenv SVN_ROOT /nfs/disks/svn_root# Step 2: 创建项目数据库根目录(Native Command)> dvc_checkout_project testcase /projects/d1tl409a# Step 3: 创建设计版本并关联外部数据> dvc_create_design P1-trial/chip/000-DATA/20240501-cust_v1> dvc_checkout_design > dvc_link_object /nfs/disks/rundir RUNDIR # 链接共享目录 > dvc_copy_object /sfs/disks/rundir/design.v design.v # 复制网表 > dvc_copy_object /sfs/disks/rundir/design.sdc design.sdc > dvc_set_dqi CELL_COUNT 11566 # 设置DQI指标(单元数量)> dvc_checkin_design3. 分步骤管理设计文件夹(多步骤流程)

场景:在APR流程中,需分步骤提交布局(Place)和时钟树综合(CTS)数据。

操作流程:

xxxxxxxxxx# Step 1: 创建设计版本> dvc_create_design P1-trial/chip/400-APR/20240601-apr_v1# Step 2: 分步骤提交布局数据> dvc_checkout_design > dvc_link_object /nfs/disks/apr/rundir RUNDIR # 链接共享目录 > dvc_create_container place # 创建布局容器 > dvc_copy_object src/design.v design.v # 复制布局网表 > dvc_copy_object src/design.sdc design.sdc > dvc_set_dqi WNS 50 # 设置时序指标(WNS=50ps) > dvc_checkin_container # 提交布局容器# Step 3: 分步骤提交时钟树数据 > dvc_create_container cts # 创建时钟树容器 > dvc_copy_object cts/design.spef design.spef > dvc_set_dqi SKEW 10 # 设置时钟偏差指标 > dvc_checkin_container # 提交时钟树容器# Step 4: 提交完整设计版本> dvc_checkin_design4. 多模式管理设计文件夹(多工艺角/电压模式)

xxxxxxxxxx# Step 1: 创建设计版本> dvc_create_design P1-trial/chip/520-STA/20240610-sta_v1# Step 2: 提交不同工艺角数据> dvc_checkout_design > dvc_create_container func/0p80V/tt_85C # 典型工艺角(0.8V, 85°C) > dvc_copy_object sta/func/design.rpt timing.rpt > dvc_set_dqi WNS 50 > dvc_checkin_container > dvc_create_container scan/0p72V/ss_125C # 慢速工艺角(0.72V, 125°C) > dvc_copy_object sta/scan/design.rpt timing.rpt > dvc_set_dqi WNS -100 > dvc_checkin_container# Step 3: 提交完整设计版本> dvc_checkin_design五、异常处理与维护

1.常见错误与解决

错误1:若用户未定义DVC_WORKING环境变量,系统将自动处理 1.提示信息:

xxxxxxxxxx[user@server] dvc project checkoutNo environment variable found : DVC_WORKING Set DVC working folder in: projuser/<project account>/DVC Checking out project 2.目录创建:

会在用户主目录(/projusers/<project_account>)下自动创建DVC文件夹(若不存在)。默认路径为:/projusers/<project_account>/DVC,其中<project_account>为当前用户账号(如d1tl409af01)。

3.项目检出(checkout):

自动执行dvc project checkout,将项目数据下载至默认路径。

解决:重新执行source命令并设置DVC_WORKING。

错误2:权限不足 1.提示信息:

xxxxxxxxxx[user@server] dvc folder create P1-trialERROR: User 'd1tl409af01' has no permission to create Phase.解决:切换至a00账号或联系项目经理(project leader)授权。

错误3:版本路径不存在 1.提示信息:

xxxxxxxxxx[user@server] dvc folder checkout P1-trial/cpu/400-APR/20240601-invalid_v1ERROR: Path 'P1-trial/cpu/400-APR/20240601_invalid_v1' does not exist in SVN.解决:1.使用svn list验证版本路径是否存在。 2.联系提交者确认版本名称或重新提交。

2.数据版本查看与版本恢复

1.查看全项目版本

xxxxxxxxxx# Step 1: 加载环境变量&创建DVC workingspace> source /lyg/projects/d1tl409a/cshrc_dop> dvc project checkout# Step 2: 查看所有版本> svn list -R svn://$SVN_HOST:$SVN_PORT/$pCode> svn list -R svn://zhuunxsvn01:11216/d1tl409a# 输出示例: P1-trial/ P1-trial/cpu/ P1-trial/cpu/200-LOGIC P1-trial/cpu/200-LOGIC/20240501-logic_v1/ P1-trial/cpu/200-LOGIC/20240501-logic_v1/... P1-trial/ddr/300-DFT/20240515-scan_v2/ P1-trial/cpu/400-APR/20240601-apr_v1/ .....2.下载期望的版本数据

xxxxxxxxxx# Step 1: 签出APR版本数据dvc folder checkout P1-trial/cpu/400-APR/20240601-apr_v1# Step 2: 验证下载内容ls P1-trial/cpu/400-APR/20240601-apr_v1# 输出示例:design.def design.spef dvc_metadata.json**可结合dqi viewer对设计质量进行检查# 进入存放数据的目录后敲打下列命令对dqi viewer进行调用> dqiviewer六、个人扩展建议

自动化脚本示例:

xxxxxxxxxx#自动提交每日设计版本source /lyg/projects/d1tl409a/cshrc_dopsetenv DVC_WORKING /projusers/$USER/DVCdvc project checkoutset version = `date +"%Y%m%d"`_daily_v1dvc folder create P1-trial/cpu/200-LOGIC/$versiondvc object copy /design/rtl/*.v P1-trial/cpu/200-LOGIC/$versiondvc dvcpath checkin P1-trial/cpu/200-LOGIC/$version多项目管理:

xxxxxxxxxx# 项目A环境source /lyg/projects/d1tl409a/cshrc_dopsetenv DVC_WORKING ~/DVC/d1tl409advc project checkout# 项目B环境source /lyg/projects/d2tl410b/cshrc_dopsetenv DVC_WORKING ~/DVC/d2tl410bdvc project checkout七、总结

通过 Wrapper Commands 的易用性与 Native Commands 的灵活性,DVC系统可完美适配半导体设计团队的全流程需求:

规范性:严格的命名规则与层级结构确保数据一致性。 高效性:从提交到审批的自动化流程减少人为错误。 可追溯性:SVN记录全生命周期操作,支持快速回滚与审计。

操作铁律: 1.始终先执行source:确保环境变量与权限正确加载。 2.遵循命名规范:从Phase到Container均需按规则命名。 3.定期检查未审批版本:使用dvc dvcpath confirmlist避免流程阻塞。