芯片设计流程标准化平台 (DOP: Design Operation Platform)

在现代电子产品设计中,ASIC / Soc实体设计已经成为不可或缺的一环。然而,由于ASIC / Soc实体设计的复杂性,往往需要大量的人力、时间和资源来实现。

面对不断增长的设计复杂性,共同设计协作是常用的解决方案,然而设计团队和团队成员常分布在不同的地理区域,面对复杂的设计、数据管理和流程整合挑战,公司常需在进度和质量之间做出取舍。且为了提高设计效率、降低设计成本,设计自动化已成为现代电路设计的一个重要方向。一般将RTL或Gate Level之网表设计转换成GDS蓝图的过程,约占整体IC设计时间的四成,且建置成本可高达数千万人民币以上,再加上昂贵的光罩费用,因此禁不起半点错误。所以如何确保品质、缩短设计流程时间成为ASIC设计公司的目标。

当前挑战与痛点

在实际的 ASIC / SoC 项目中,团队每天都在回答几件看似简单、却反复出现的问题:

1. 我们是不是都在用同一份设计资料?

2. 当前这个版本,质量到底怎么样,能不能作为后续工作的输入?

3. 从 RTL 到 signoff 的关键步骤,是不是每次都按照同一个流程、不会漏步骤?

4. 使用的 PDK、标准单元库、IP 等技术资料,是不是受控版本、环境一致?

因此我们开发了一个芯片设计流程标准化平台 ( DOP: Design Operation Platform ) ,取代人工的品质验证与流程串接,并透过资料收集,让系统判断品质,同时减少人为疏失而导致的无形成本。简而言之,本系统将专案执行所需的纪律、细节、品质…等等,实践成自动化系统,并能透过资料收集,让系统和流程自我成长,提高设计部门的效率。

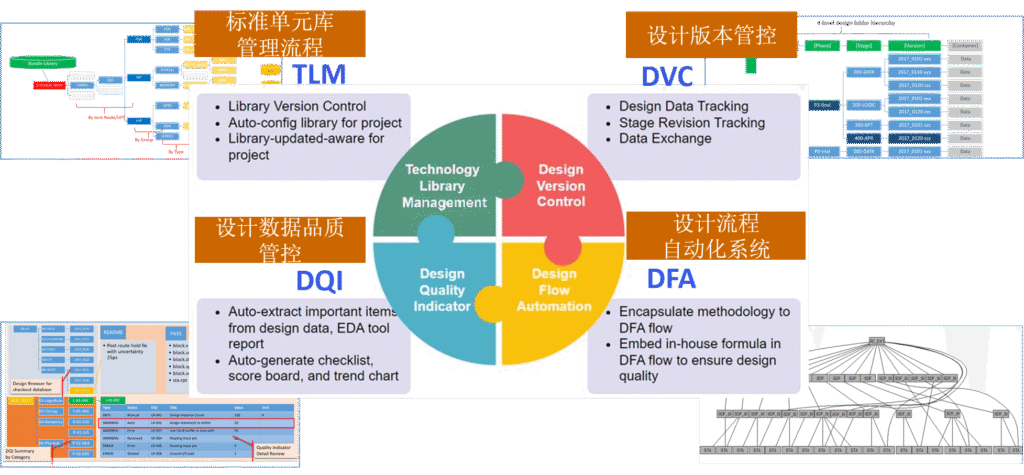

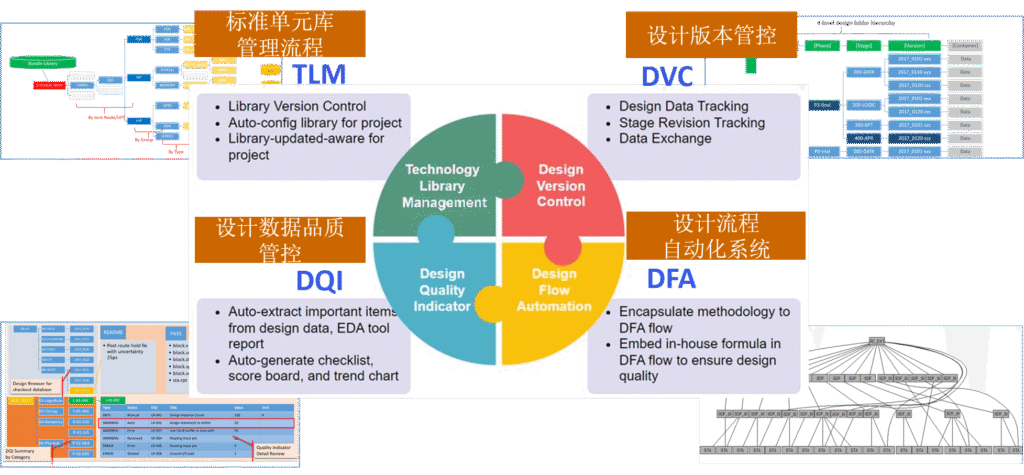

芯片设计流程标准化平台(DOP: Design Operation Platform)是一种基于EDA技术的软件系统,可以自动化设计流程的各个阶段。该系统包括了设计流程规划、设计资源管理、设计品质控制、设计流程优化等多个模块。通过对设计流程进行规划和管理,系统可以实现高效、稳定的设计流程。同时通过品质控制和优化,可以提高设计品质,降低设计成本。该系统由四个子系统组合而成,分别是:

DOP 并不试图替代现有的 EDA 工具,而是作为它们之上的一层**「设计运营平台」**, 负责把版本、质量、流程和技术库整合成一个可管理、可审计的整体。

四大关键模块功能

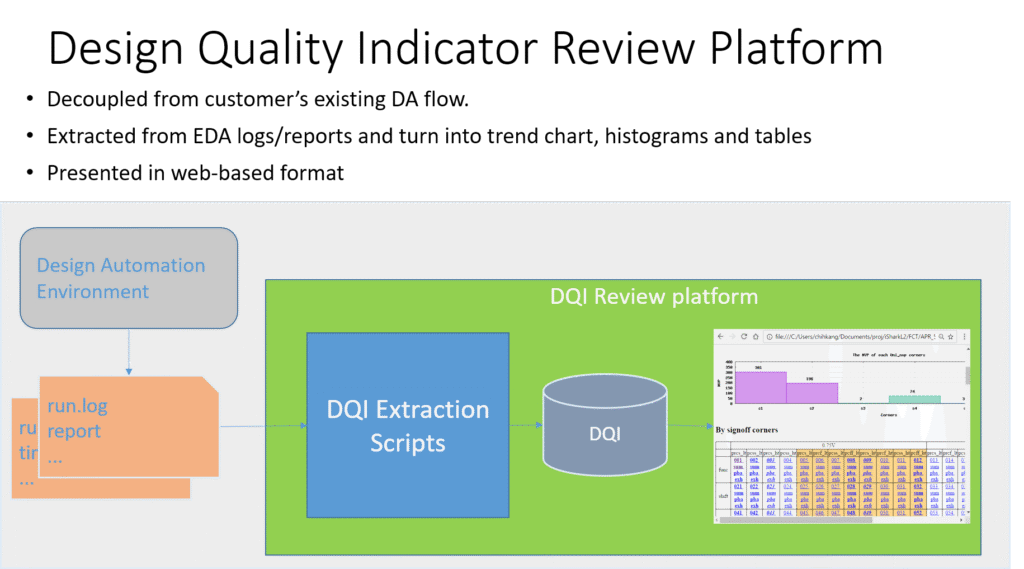

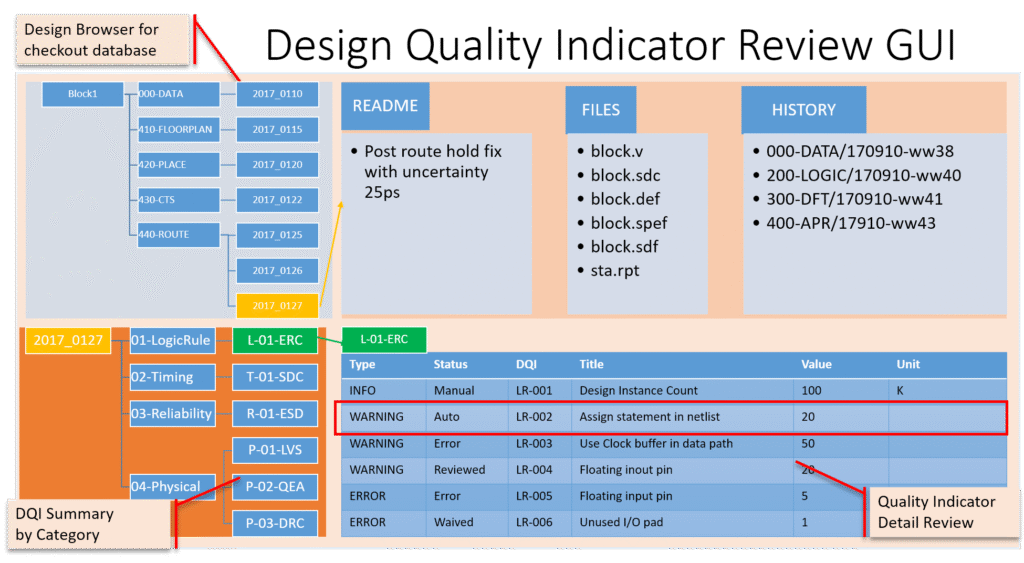

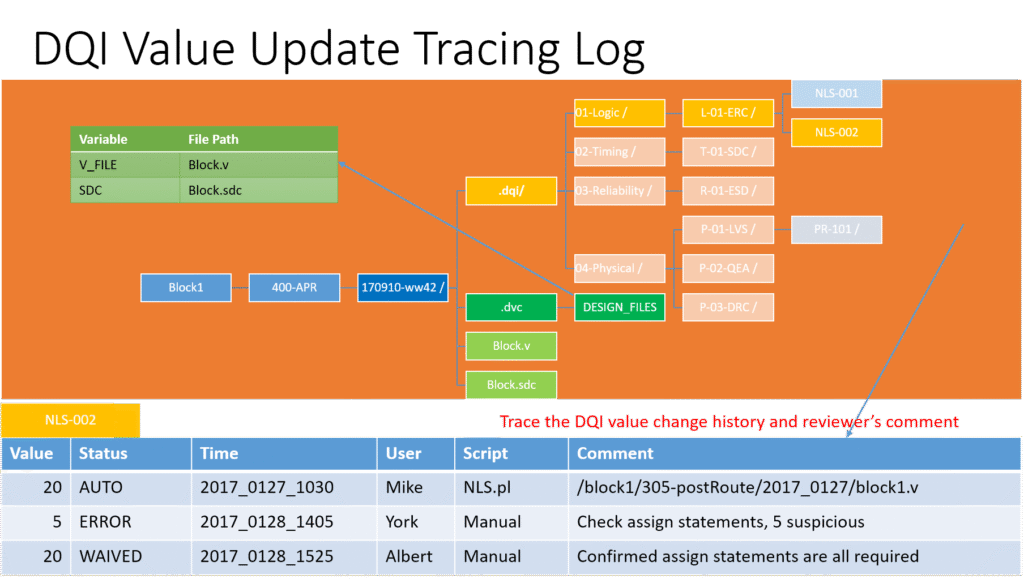

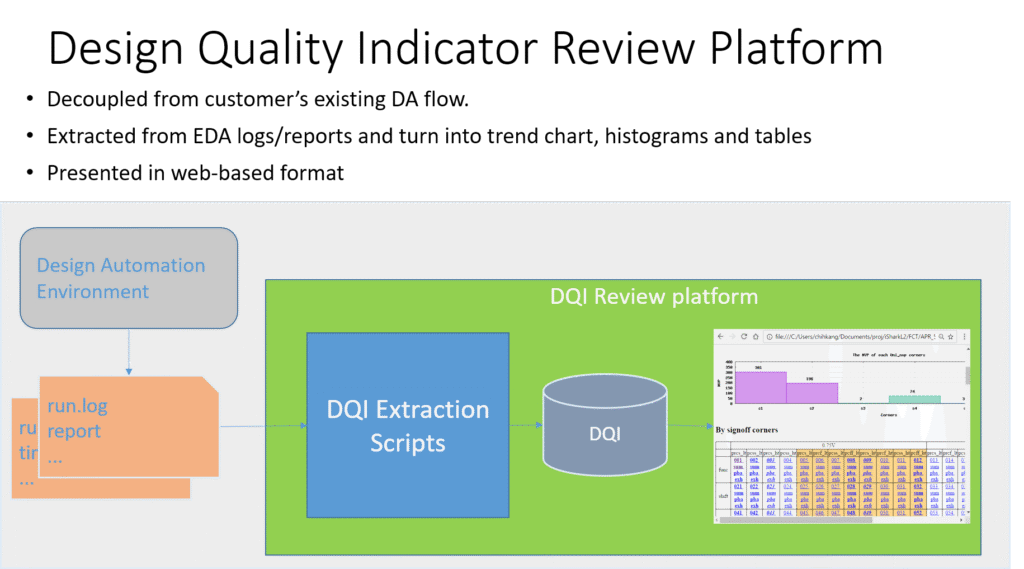

设计数据品质管控(DQI: Design Quality Indicator)

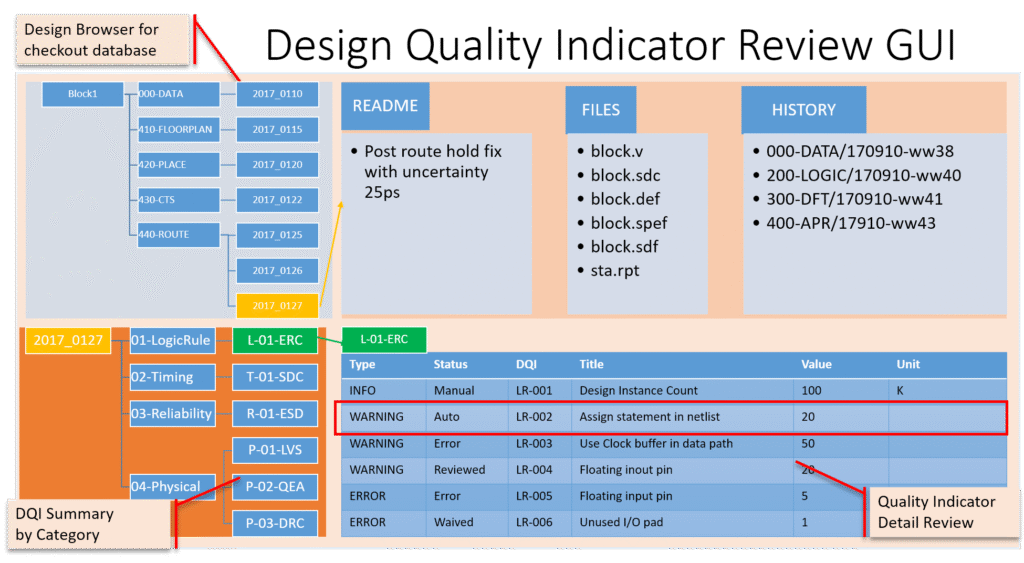

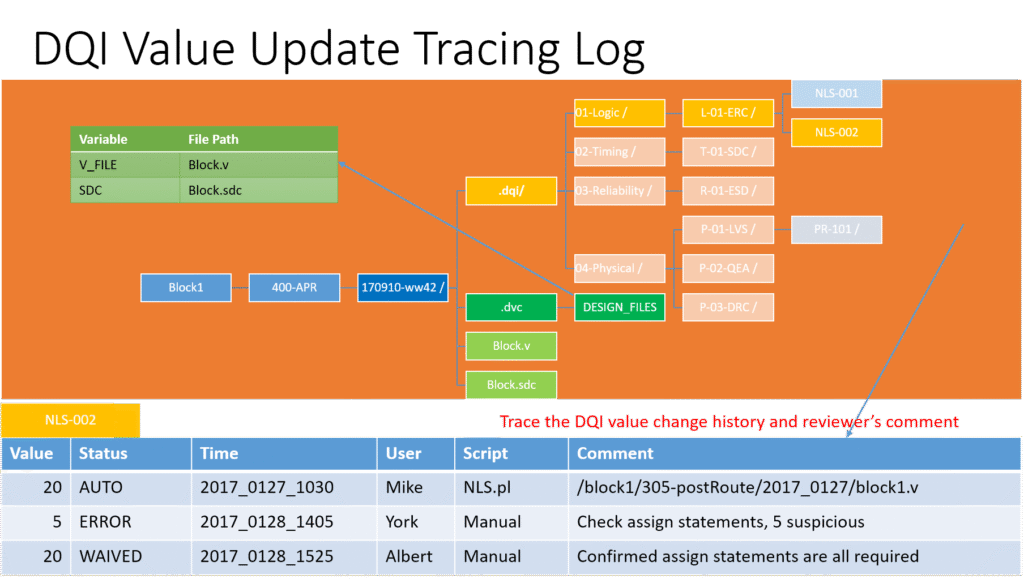

· – 从 EDA 工具报告与 log 中萃取 DQI 信息

· – 自动产生趋势图、统计图与表格

· – 提供 Web GUI 接口,便于品管与审查人员检视与回馈

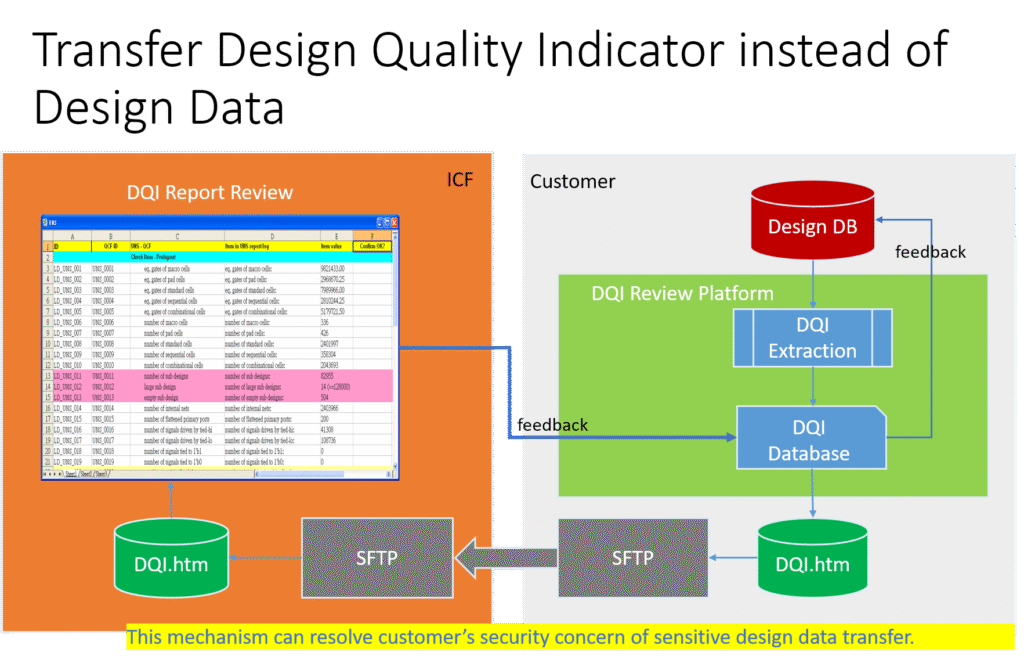

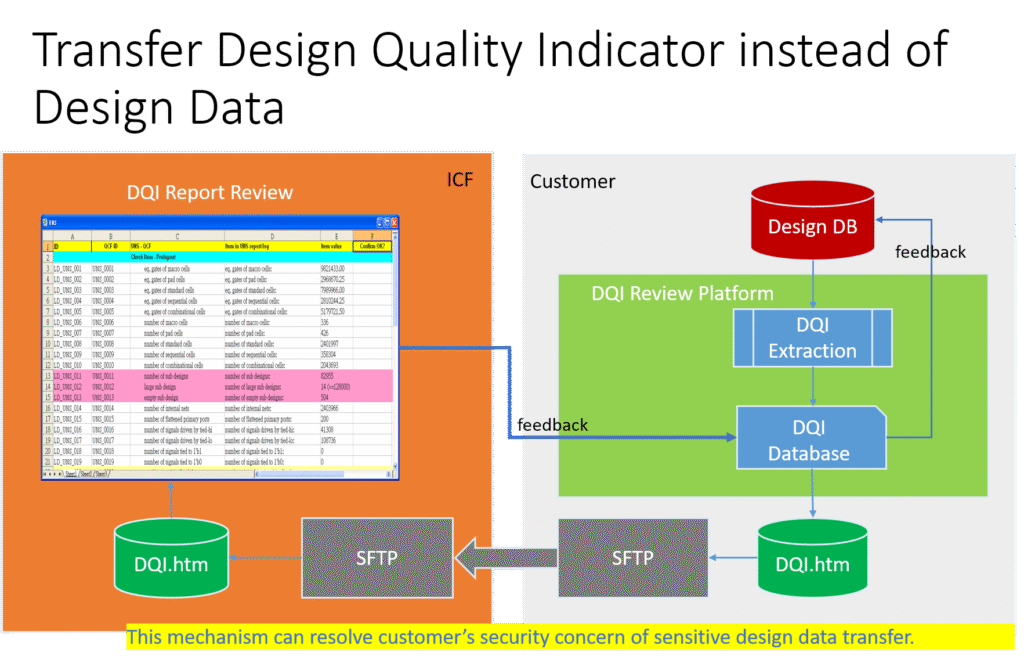

· – 传递的是「质量指针」,非完整设计数据,保障机密性

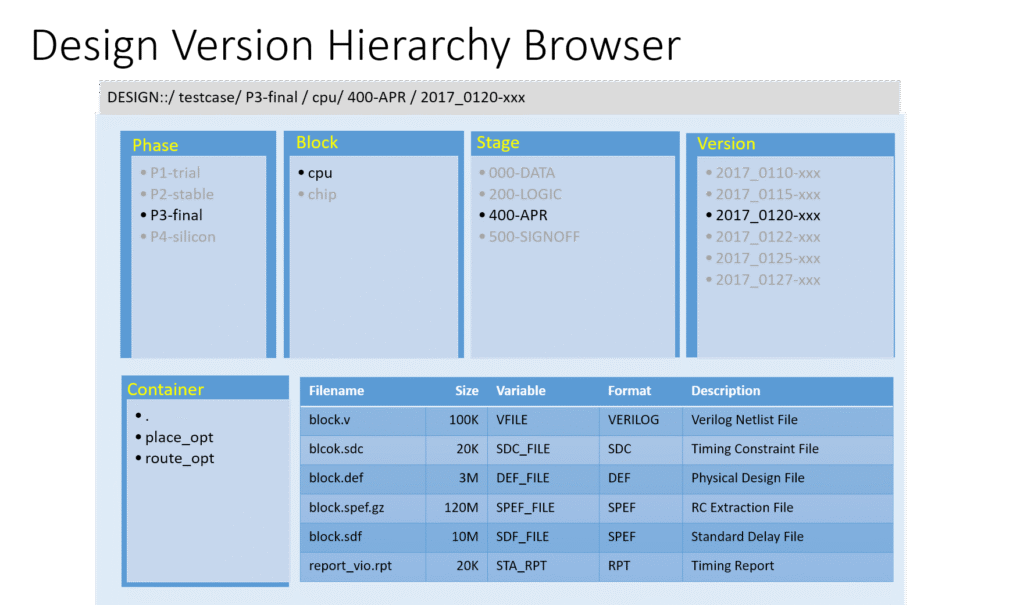

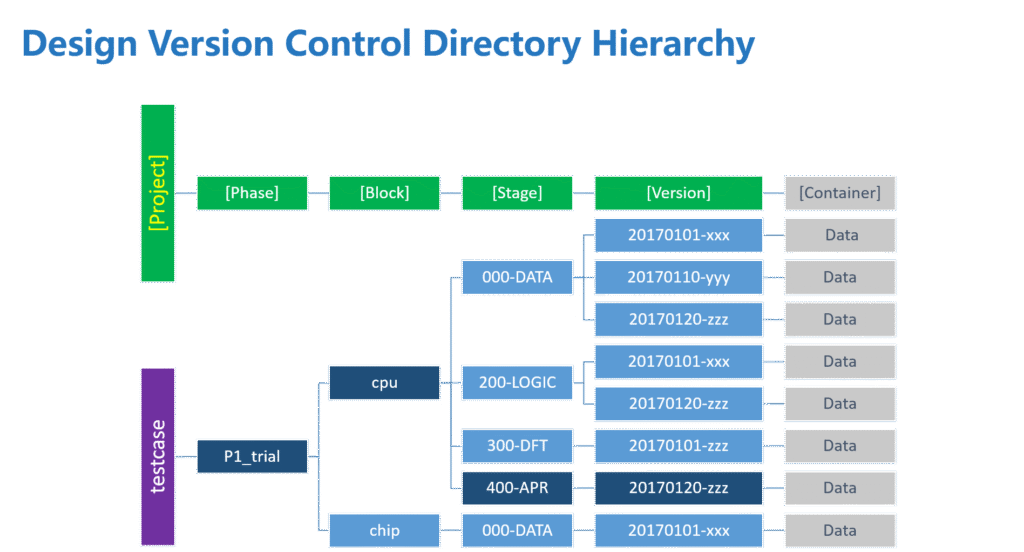

设计版本管控(DVC: Design Version Control)

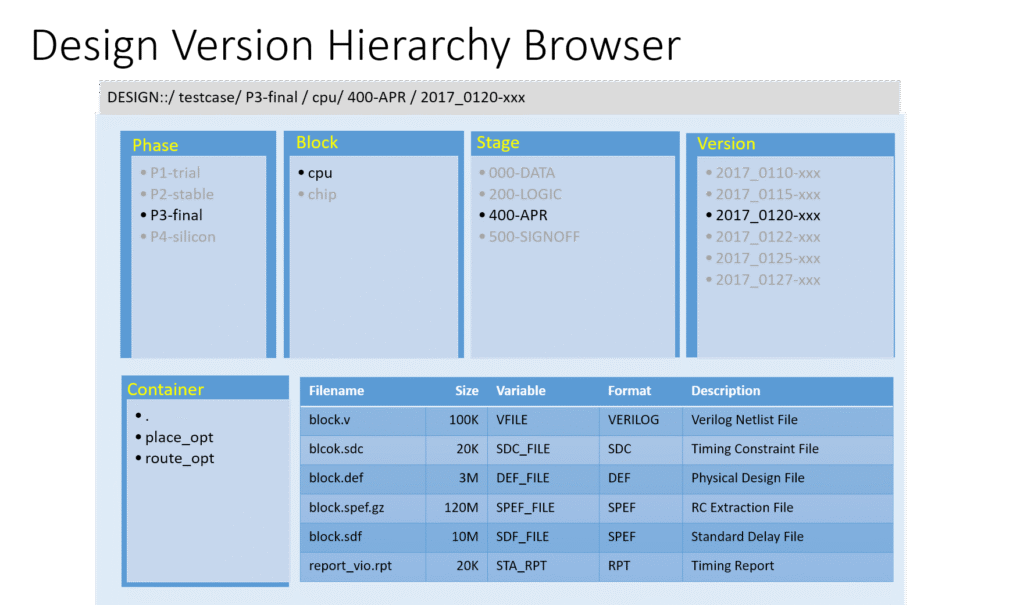

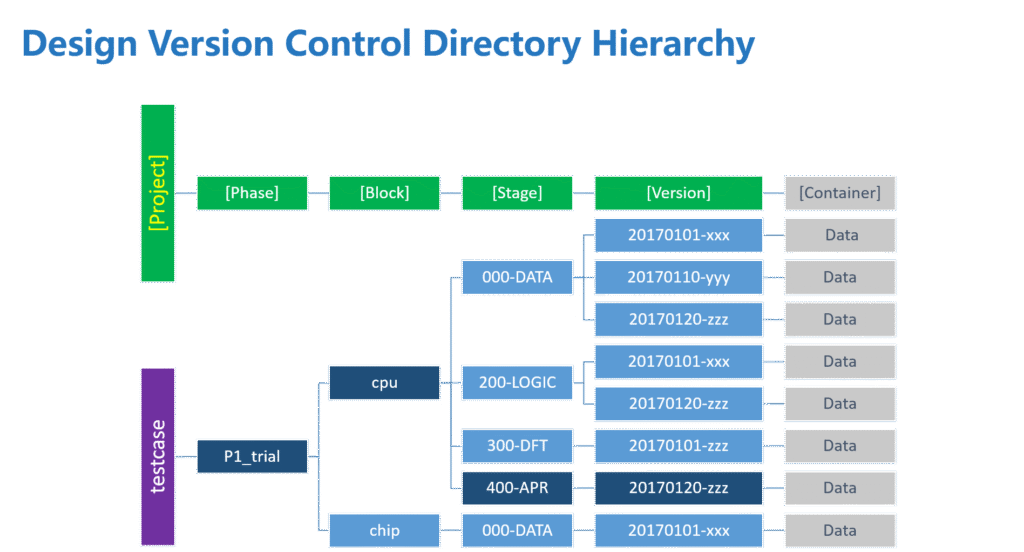

- 建立 4 层级设计文件夹架构(Phase → Block → Stage → Version)

- 每笔数据库皆能追踪 ECO 纪录与设计修改历程

- 提供 checkout、restore 等版本操作机制

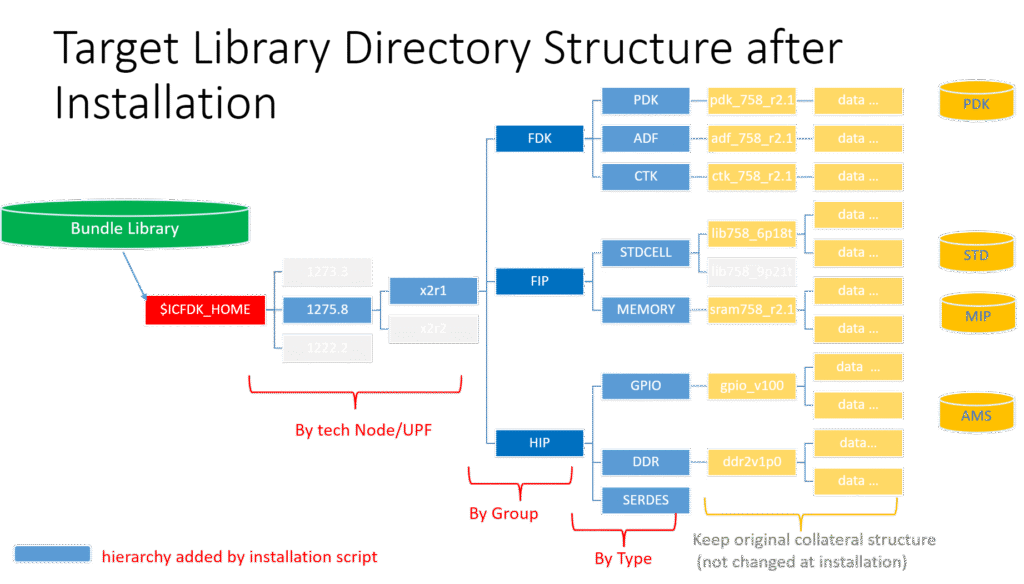

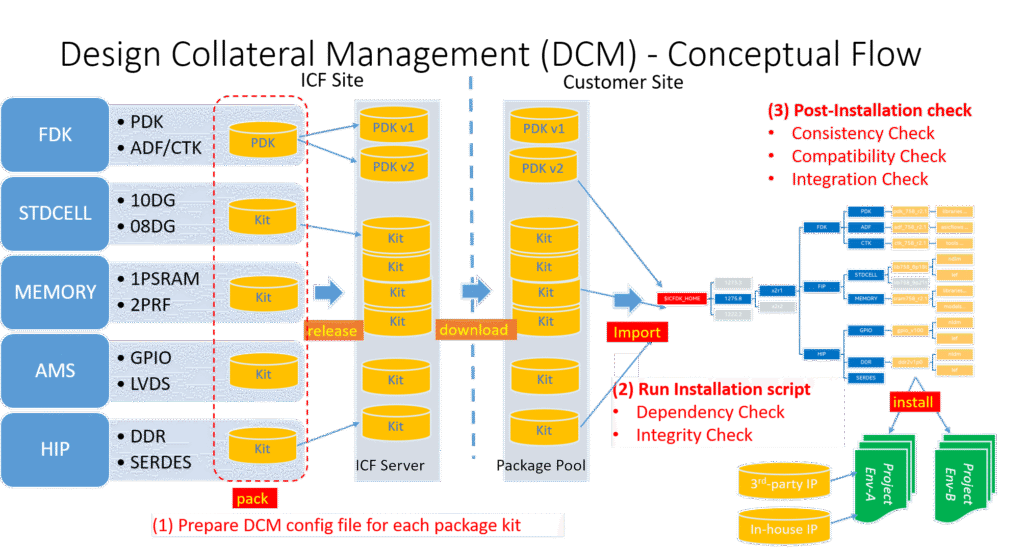

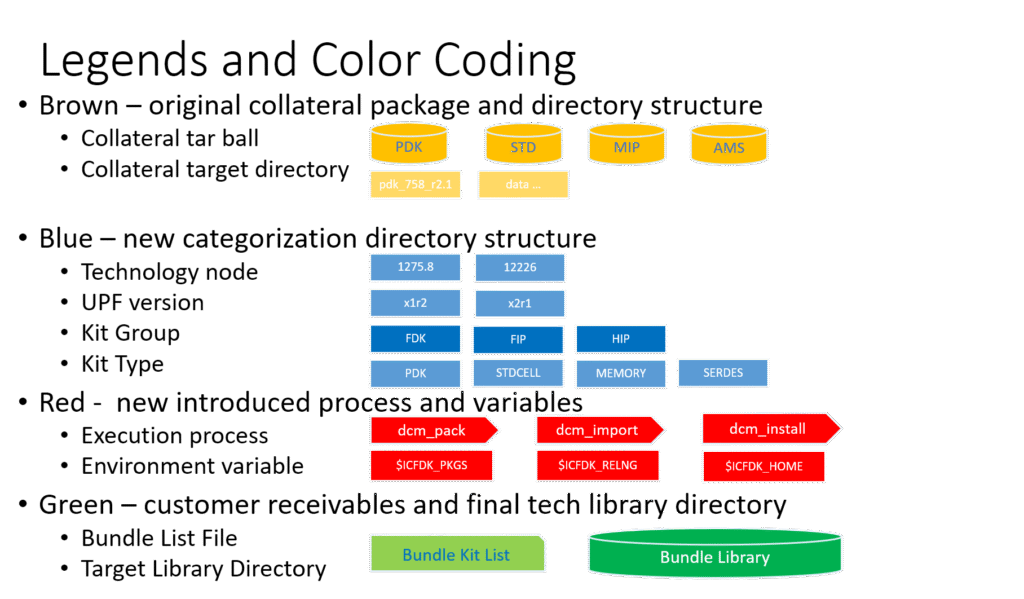

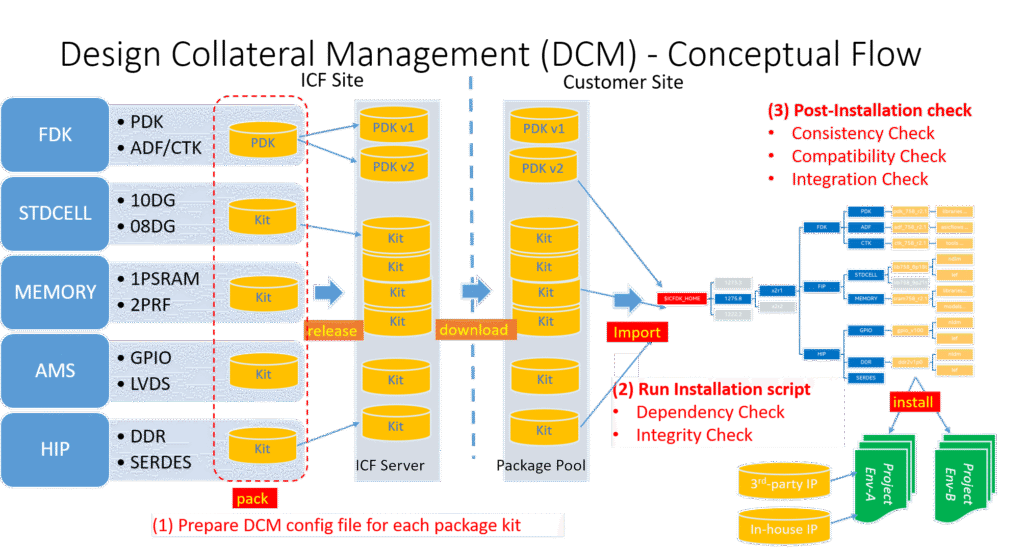

标准库管理流程(TLM: Technology Library Management)

· – 安装并管理 PDK 与 Library 套件

· – 依据技术节点与项目阶段配置 Library Bundle

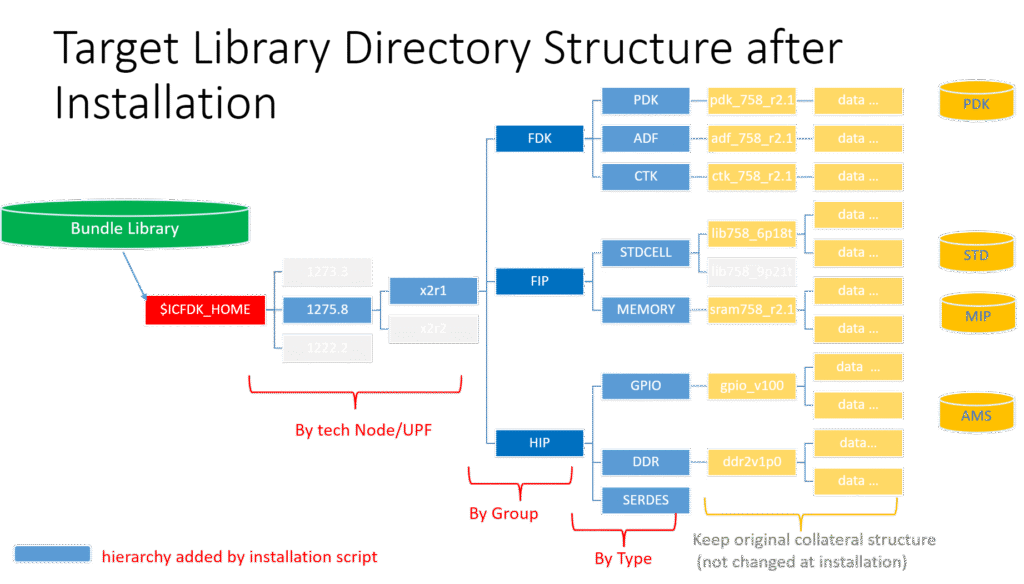

· – 维持原始 collateral 结构,导入自动化分类与验证流程

· – 安装流程自动化:汇入 → 安装 → 打包 → 发布

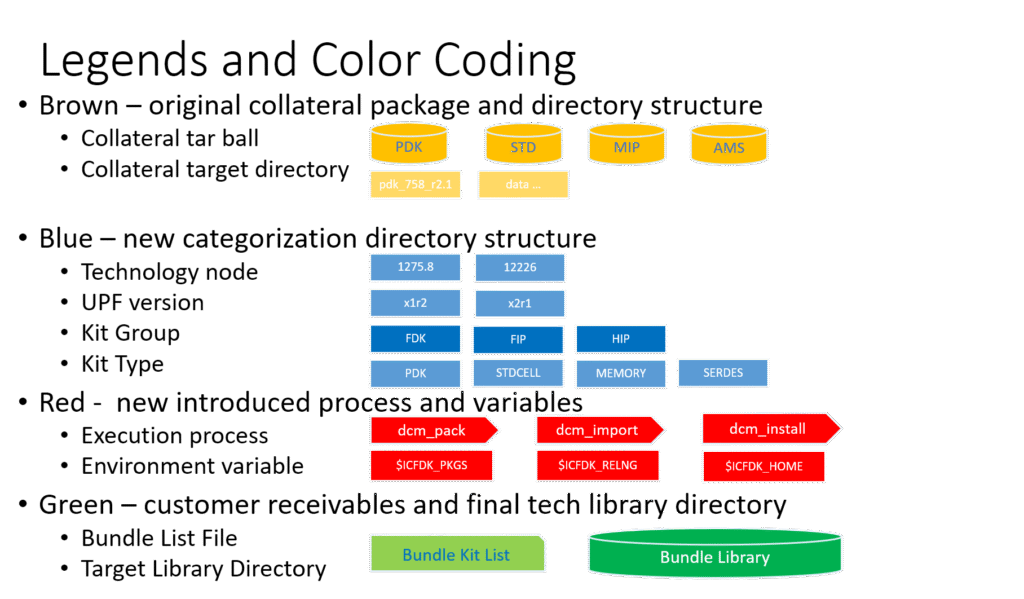

技术特色:目标数据结构与流程导图

– 保留源文件结构,透过安装脚本加入阶层分类

– 依技术节点、UPF 版本、类型等分类标准建立数据目录

– 支持客户与内部环境同步配置,确保交付一致性

安全设计:敏感数据保障机制

透过 DQI 替代设计数据的传递方式,使得客户可只传输质量指标而非完整数据库,降低数据外泄风险,满足保密与审查需求。

结语

DOP 平台为 IC 设计团队提供一个系统化、标准化的合作环境,横跨设计数据管理、流程整合与质量控管。

透过 TLM、DVC、DQI 等模块的协同运作,不仅提升设计可重现性,也大幅降低跨部门与跨据点的沟通成本,是推动智能化设计管理的核心工具。